DEVELOPER INFO

GENERAL INFORMATION

XSCHEM uses layers for its graphics, each layer is a logical entity defining graphic attributes like color and fill style. There are very few graphical primitive objects:

- Lines

- Rectangles

- Open / close Polygons

- Arcs / Circles

- Text

These primitive objects can be drawn on any layer. XSCHEM number of layers can be defined at compile time, however there are some predefined layers (from 0 to 5) that have specific functions:

- Background color

- Wire color (nets)

- Selection color / grid

- Text color

- Symbol drawing color

- Pin color

- General purpose

- General purpose

- General purpose

....

- General purpose

- General purpose

Although any layer can be used for drawing it is strongly advisable to avoid the background color and the selection color to avoid confusion. Drawing begins by painting the background (layer 0), then drawing the grid (layer 1) then drawing wires (nets) on layer 2, then all graphical objects (lines, rectangles, polygons) starting form layer 0 to the last defined layer.

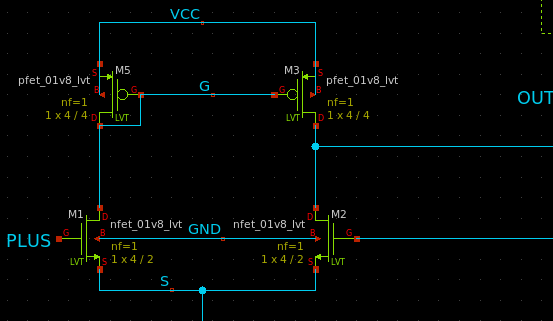

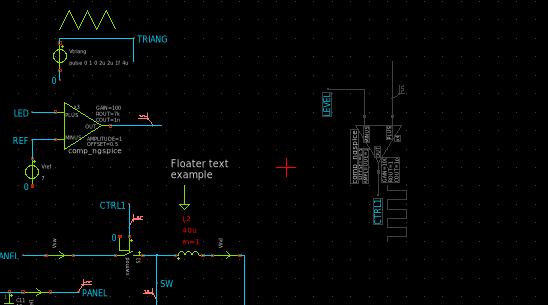

SYMBOLS

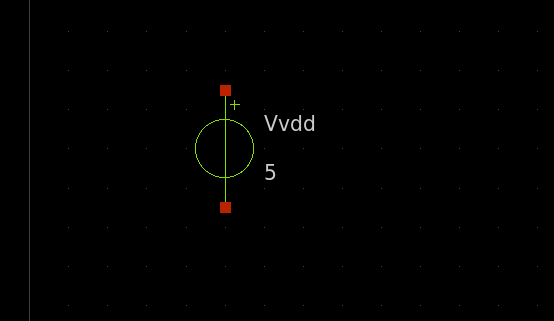

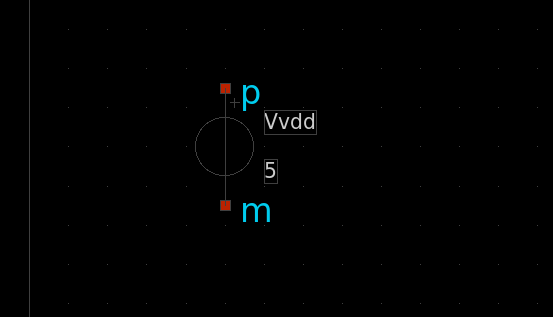

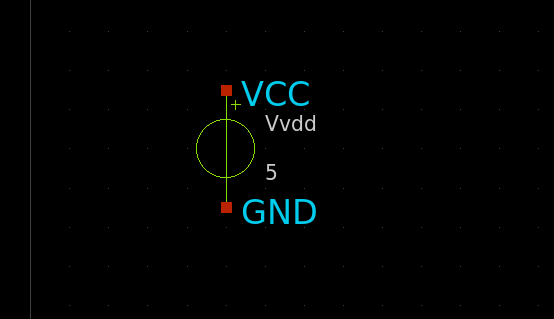

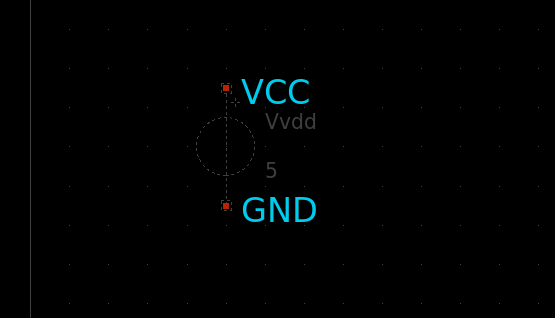

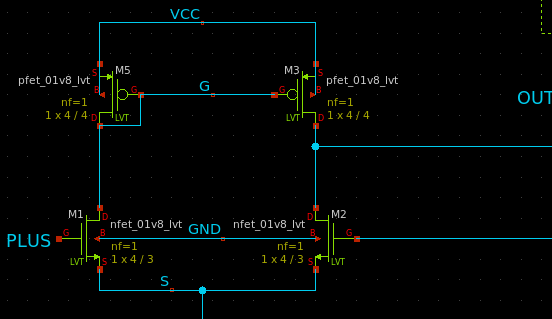

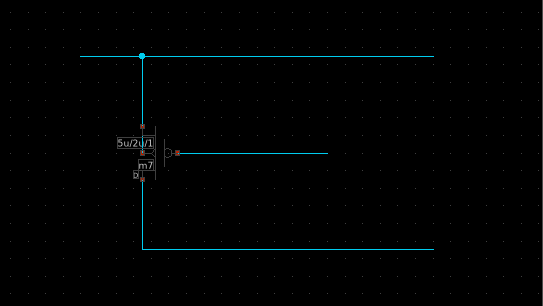

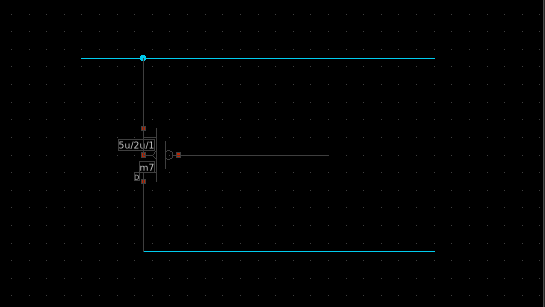

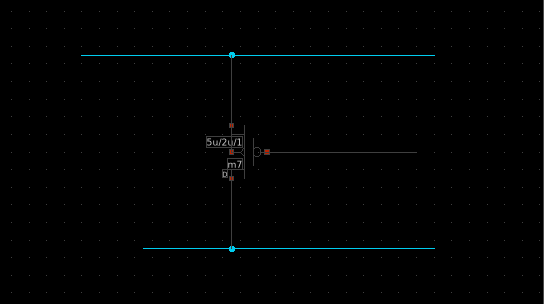

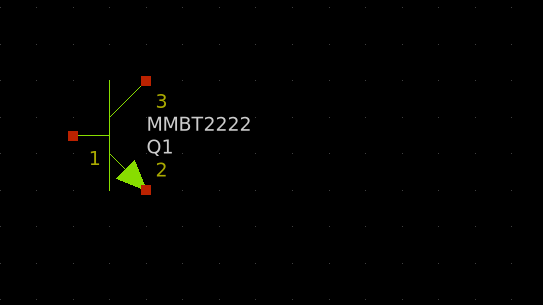

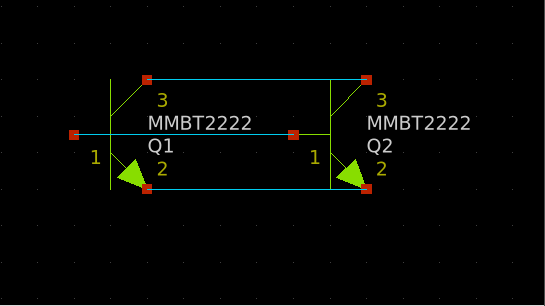

There is a primitive object called symbol. Symbols are just a group of primitive graphic objects (lines, polygons, rectangles, text) that can be shown as a single atomic entity. Once created a symbol can be placed in a schematic. The instantiation of a symbol is called 'component'.

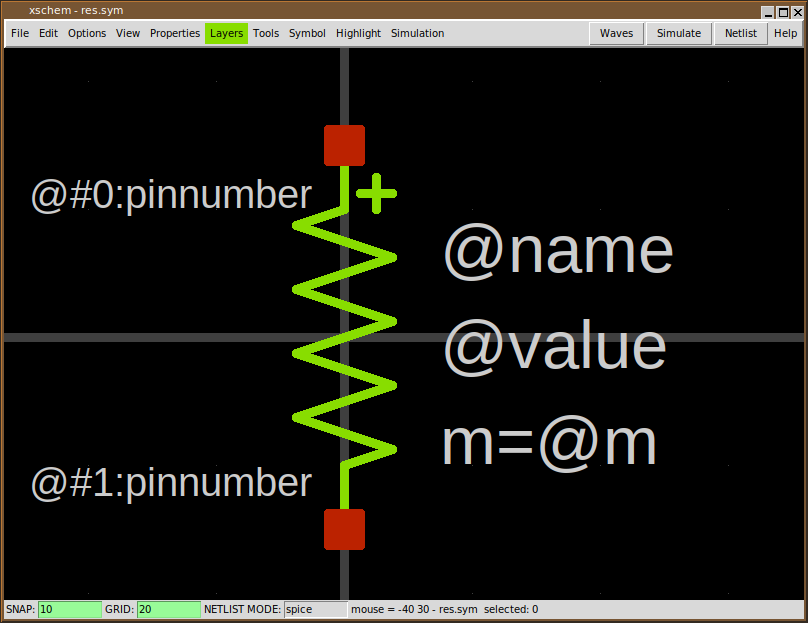

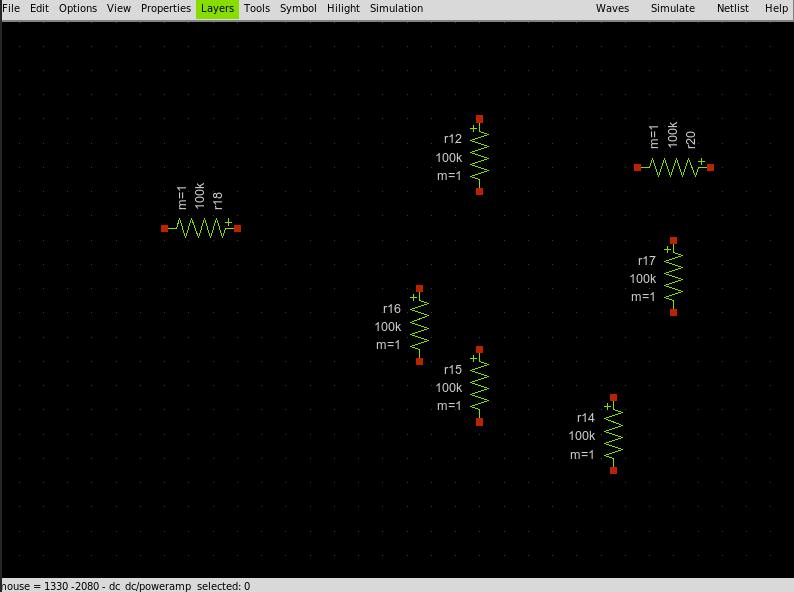

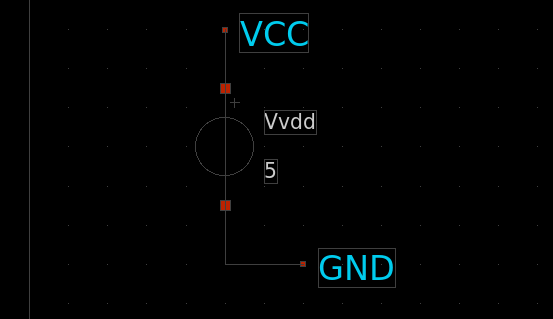

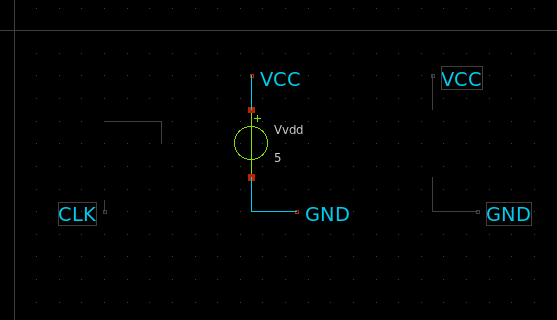

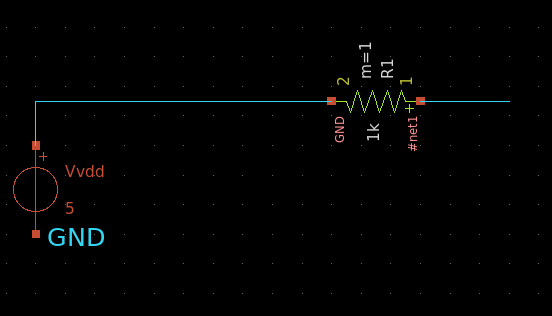

The above picture shows a resistor symbol, built drawing some lines on layer 4 (green), some pins on layer 5 (red) and some text. Symbols once created are stored in libraries (library is just a UNIX directory known to XSCHEM) and can be placed like just any other primitive object multiple times in a schematic window with different orientations.

WIRES

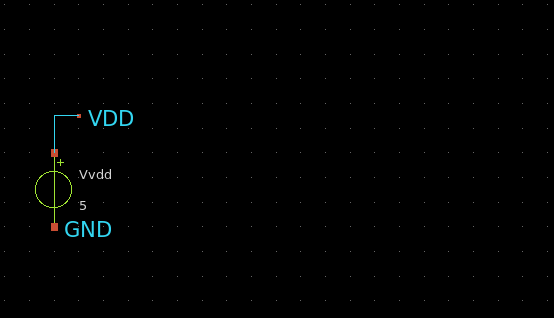

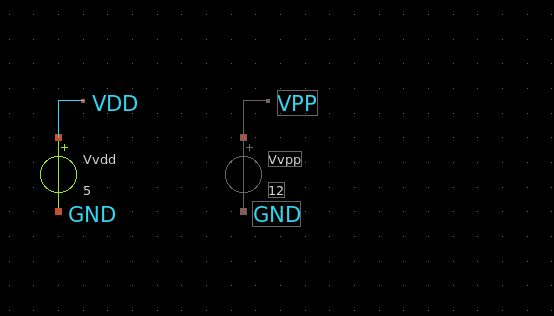

Another special primitive object in XSCHEM is 'Wire', Graphically it is drawn as a line on layer 1 (wires). Wires are drawn only on this layer, they are treated differently by XSCHEM since they carry electrical information. Electrical connection between components is done by drawing a connecting wire.

Since wires are used to build the circuit connectivity it is best to avoid drawing lines on layer 1 to avoid confusion, since they would appear like wires, but ignored completely for electrical connectivity.

PROPERTIES

All XSCHEM objects (wires, lines, rectangles, polygons, text, symbol instance aka component) have a property string attached. Any text can be present in a property string, however in most cases the property string is organized as a set of key=value pairs separated by white space. In addition to object properties the schematic or symbol view has global properties attached. There is one global property defined per netlisting mode (currently SPICE, VHDL, Verilog, tEDAx, Spectre) and one additional global property for symbols (containing the netlisting rules usually). See the XSCHEM properties section of the manual for more info.

COORDINATE SYSTEM

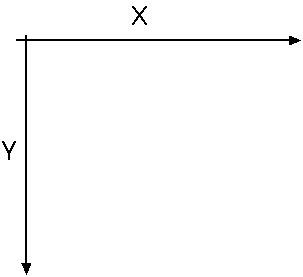

XSCHEM coordinates are stored as double precision floating point numbers, axis orientation is the same as Xorg default coordinate orientation:

When drawing objects in XSCHEM coordinates are snapped to a multiple of 10.0 coordinate units, so all drawn objects are easily aligned. The snap level can be changed to any value by the user to allow drawing small objects if desired. Grid points are shown at multiples of 20.0 coordinate units, by default.

XSCHEM FILE FORMAT SPECIFICATION

XSCHEM schematics and symbols are stored in .sch and .sym files respectively. The two file formats are identical, with the exception that symbol (.sym) files usually do not contain wires and component instantiations (although they can).

every schematic/symbol object has a corresponding record in the file. A single character at the beginning of a line, separated by white space from subsequent fields marks the type of object:

- v : XSCHEM Version string

- S : Global property associated to the .sch file for SPICE netlisting

- V : Global property associated to the .sch file for VERILOG netlisting

- F : Global property associated to the .sch file for SPECTRE netlisting (file format 1.3 and newer)

- G : Global property associated to the .sch file for VHDL netlisting OR Global property associated to the .sym file for netlisting (in 1,2 file format K is used, although backward compatibility is guaranteed)

- E : Global property associated to the .sch file for tEDAx netlisting

- K : Global property associated to the .sch/sym file for netlisting.

For schematic it is used if instantiated as a component (file format 1.2 and newer) - L : Line

- B : Rectangle

- P : Open / Closed polygon

- A : Arc / Circle

- T : Text

- N : Wire, used to connect together components (only in .sch files)

- C : Component instance in a schematic (only in .sch files)

- [ : Start of a symbol embedding, the symbol refers to the immediately preceding component instance. This tag must immediately follow a component instance (C). See the example here under. A component symbol is embedded into the schematic file when saving if the embed=true attribute is set on one of the component instances. Only one copy of the embedded symbol is saved into the schematic and all components referring to this symbol will use the embedded definition. When a component has an embedded symbol definition immediately following, a embed=true is added to the component property string if not already present.

C {TECHLIB/PCH} 620 -810 0 0 {name=x5 model=PCHLV w=4 l=0.09 m=1 embed=true}

[

v {xschem version=2.9.7 file_version=1.2}

G {}

K {type=pmos

format="@name @pinlist @model w=@w l=@l m=@m"

verilog_format="@verilog_gate #(@del ) @name ( @@d , @@s , @@g );"

template=" name=x1 verilog_gate=pmos del=50,50,50 model=PCH w=0.68 l=0.07 m=1 "

generic_type="model=string"

}

V {}

S {}

E {}

L 4 5 20 20 20 {}

L 4 20 20 20 30 {}

L 4 5 -20 20 -20 {}

L 4 20 -30 20 -20 {}

L 4 -20 0 -10 0 {}

L 4 5 -27.5 5 27.5 {11}

L 4 5 -5 10 0 {}

L 4 5 5 10 0 {}

L 4 10 0 20 0 {}

L 18 -2.5 -15 -2.5 15 {}

B 5 17.5 27.5 22.5 32.5 {name=d dir=inout}

B 5 -22.5 -2.5 -17.5 2.5 {name=g dir=in}

B 5 17.5 -32.5 22.5 -27.5 {name=s dir=inout}

B 5 17.5 -2.5 22.5 2.5 {name=b dir=in}

A 4 -6.25 0 3.75 270 360 {}

T {@w/@l*@m} 7.5 -17.5 0 0 0.2 0.2 {}

T {@name} 7.5 6.25 0 0 0.2 0.2 {999}

T {@model} 2.5 -27.5 0 1 0.2 0.2 {layer=8}

T {D} 25 17.5 0 0 0.15 0.15 {layer=13}

T {NF=@nf} -5 -15 0 1 0.15 0.15 {}

]

the object tag in column 1 is followed by space separated fields that completely define the corresponding object.

VERSION STRING

Example:

v {xschem version=3.4.7 file_version=1.3}

Two attributes are defined, the xschem version and the file format version. Current file format version is 1.3. This string is guaranteed to be the first one in XSCHEM .sch and .sym files. A comment can be added (by manually editing the xschem schematic or symbol file) as shown below:

v {xschem version=3.1.0 file_version=1.2

* Copyright 2022 Stefan Frederik Schippers

*

* Licensed under the Apache License, Version 2.0 (the "License");

* you may not use this file except in compliance with the License.

* You may obtain a copy of the License at

*

* https://www.apache.org/licenses/LICENSE-2.0

*

* Unless required by applicable law or agreed to in writing, software

* distributed under the License is distributed on an "AS IS" BASIS,

* WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

* See the License for the specific language governing permissions and

* limitations under the License.

}

GLOBAL SCHEMATIC/SYMBOL PROPERTIES

Example:

K {type=regulator

format="x@name @pinlist r@symname"

verilog_format="assign @#2 = @#0 ;"

tedax_format="footprint @name @footprint

device @name @symname"

template="name=U1 footprint=TO220"}

Global properties define a property string bound to the parent schematic/symbol file,

there is one global property record per netlisting mode,

currently SPICE, VHDL, Verilog, tEDAx, Spectre.

In addition (only in file_format 1.2 and newer) for schematics and symbols there is a global attribute ('K')

that defines how to netlist the schematic/symbol if placed as a

symbol into another parent schematic (should be set in the same way as the 'G' global attribute for symbols

in pre-1.2 file format).

Normally only 'G' ('K' in 1.2 file format) type property strings are used for symbols and define attributes

telling netlisters what to do with the symbol, while global property

strings in schematic files corresponding to the active netlisting mode of XSCHEM are

copied verbatim to the netlist.

File formats 1.3 and newer introduce also the SPECTRE global attribute ('F') for Spectre netlists.

the object tag (S, V, G, E, F, K) is followed by the property string enclosed in curly braces

({...}). This allows strings to contain any white space and newlines.

Curly braces if present in the string are automatically escaped with the '\' character

by XSCHEM when saving data.

Example of the 4 property string records for a schematic file:

G {}

V {assign #1500 LDOUT = LDIN +1;

}

E {}

S {}

in this case only the verilog-related global property has some definition. This is Verilog code that is copied into the output netlist.

Attribute strings for all Xschem objects are enclosed in curly braces.

This allows attributes to span multiple lines.

This component instance:

C {capa.sym} 890 -160 0 0 {name=C4 m=1 value=10u device="tantalium capacitor"}

and this one:

C {capa.sym} 890 -160 0 0 {name=C4

m=1 value=10u

device="tantalium capacitor"

}

are perfectly equivalent.

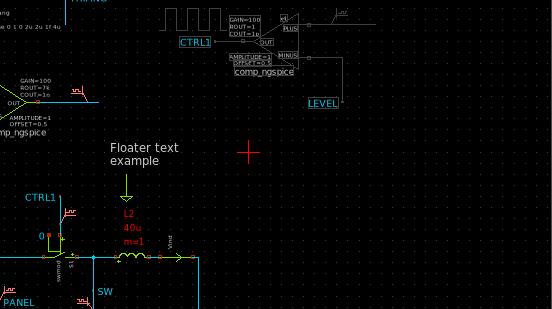

TEXT OBJECT

Example: T {3 of 4 NANDS of a 74ls00} 500 -580 0 0 0.4 0.4 {font=Monospace layer=4}

This line defines a text object, the first field after the type tag is the displayed text,

followed by X and Y coordinates,rotation, mirror,

horizontal and vertical text size and finally a property string defining some text attributes.

- The displayed text is enclosed in curly braces ({...}) to allow white space. Literal curly braces must be escaped if present in the saved string. XSCHEM will automatically add the escapes where needed on save.

- X ad Y coordinates are saved and retrieved as double precision floating point numbers.

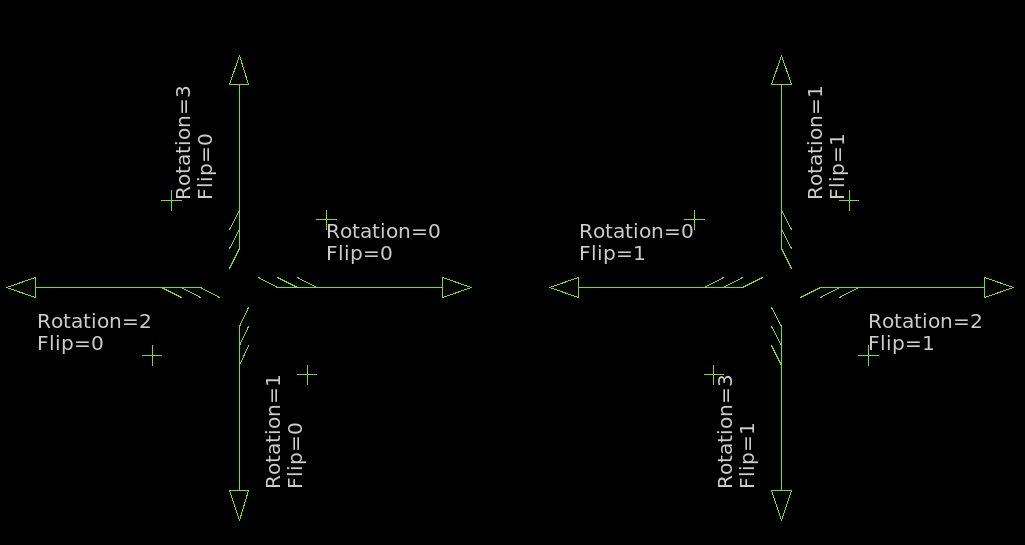

- Rotation and mirror are integers (range [0:3], [0:1] respectively) that define the orientation

of text objects. Using rotation and mirror text can be aligned to any corner of its bounding box, so there are 4 different

alignments for vertical text and 4 different alignments for horizontal text. Below picture shows how text is displayed

with respect to its anchor point.

- text X and Y sizes are stored as floating point numbers.

- Finally a property string is available to attach attributes to the text object.

Currently the following attributes are predefined for text objects:

- font Name of font to be used (ex: font=Arial)

- layer Number of layer to use for drawing (as in Xschem Layers menu)

- hcenter If set to true horizontal center text

- vcenter If set to true vertical center text

- weight If set to bold use bold style

- slant If set to italic or oblique use that style for text

- hide If set to true text will be hidden unless View->Show hidden texts

is enabled

If hide=instance is given the text will be invisible in placed instances of the symbol, but visible when descending into the symbol.

WIRE OBJECT

Example: N 890 -130 890 -110 {lab=ANALOG_GND}

Format: N x1 y1 x2 y2 {attributes}

The net 'N' tag is followed by the end point coordinates x1,y1 - x2,y2.

(stored and read as double precision numbers) and a property string, used in this case to name the net.

In most cases you don't need to specify attributes for nets (one exception is the bus attribute)

as the lab attribute is set by xschem when creating a netlist or more generally when

building the connectivity.

This means that almost always nets in a xschem schematic are set as in following example:

N 890 -130 890 -110 {}

Xschem schematic files store only geometrical data and attributes of the graphic primitives,

the connectivity and the logical network is obtained by xschem.

LINE OBJECT

Example: L 4 -50 20 50 20 {This is a line on layer 4}

Format: L layer x1 y1 x2 y2 {attributes}

The line 'L' tag is followed by an integer specifying the graphic layer

followed by the x1,y1 - x2,y2 coordinates of the line and a property string.

RECTANGLE OBJECT

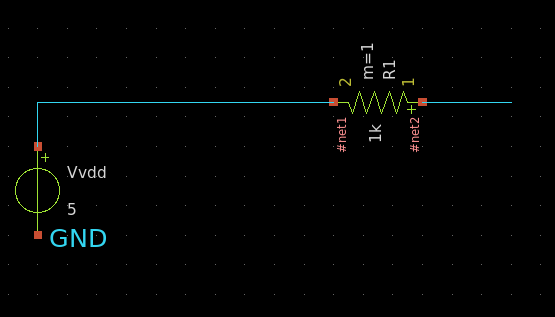

Example: B 5 -62.5 -2.5 -57.5 2.5 {name=IN dir=in pinnumber=1}

Format: B layer x1 y1 x2 y2 {attributes}

The 'Box' 'B' tag is followed by an integer specifying the graphic layer followed

by the x1,y1 - x2,y2 coordinates of the rectangle

and a final property string. This example defines a symbol pin.

A fill=true attribute may be given get a patterned fill (this is the default for rectangles).

A fill=false attribute may be given to avoid a fill pattern.

A fill=full attribute may be given to get a full solid fill.

Example: B 4 100 -300 400 100 {fill=false}

OPEN / CLOSED POLYGON OBJECT

Example: P 3 5 2450 -210 2460 -170 2500 -170 2510 -210 2450 -210 {}

Format: P layer npoints px1 py1 px2 py2 .... {attributes}

the Polygon 'P' tag is followed by an integer specifying the layer number,

followed by the number of points (integer),

the x,y coordinates of the polygon points and the property string (empty in this example).

If the last point is coincident to the first point a closed polygon is drawn.

A fill=true attribute may be given to fill a closed polygon, in this case a polygon line looks like:

P 3 5 2450 -210 2460 -170 2500 -170 2510 -210 2450 -210 {fill=true}

A fill=full attribute will paint the polygon with a solid full color (instead of a patterned fill).

A bezier=true attribute will transform the polygon into a bezier curve. See

the editor commands page on polygons.

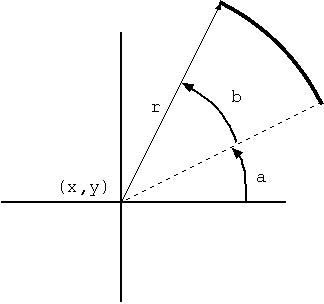

ARC OBJECT

Example: A 3 450 -210 120 45 225 {}

Format: A x y r a b {attributes}

The Arc 'A' tag is followed by an integer specifying the layer number, followed by the arc x, y center coordinates,

the arc radius, the start angle (measured counterclockwise from the three o'clock direction), the arc sweep angle

(measured counterclockwise from the start angle) and the property string (empty in this example).

Angles are measured in degrees.

Arcs can be filled or not:

A fill=true attribute may be given get a patterned fill.

A fill=false attribute may be given to avoid a fill pattern. This is the default

A fill=full attribute may be given to get a full solid fill.

Circles are just arcs with a sweep angle of 360 degrees.

Example: A 4 100 -40 40 0 360 {fill=full}

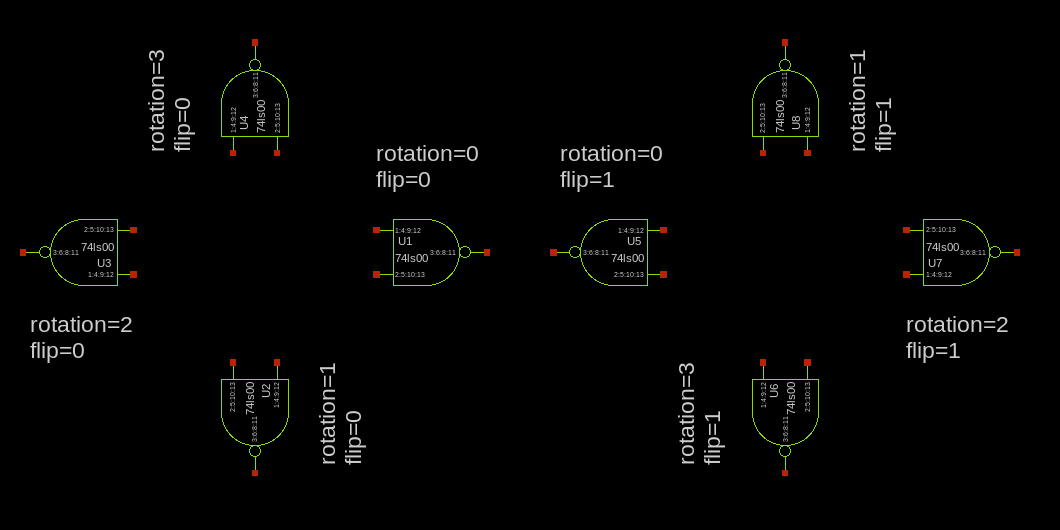

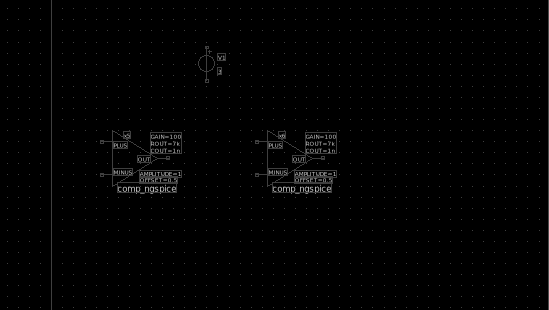

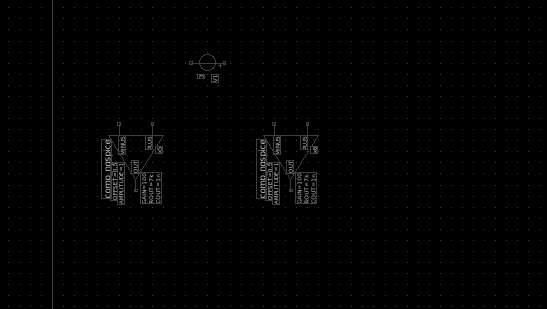

COMPONENT INSTANCE

Example: C {capa.sym} 890 -160 0 0 {name=C4 m=1 value=10u device="tantalium capacitor"}

Format: C {<symbol reference>} <X coord> <Y coord> <rotation>

<flip> {<attributes>}

The component instance tag C is followed by a string specifying library/symbol or only symbol

(see This tutorial about symbol references)

followed by the x,y coordinates, rotation (integer range [0:3]),

mirror (integer range [0:1]), and a property string defining various attributes

including the mandatory name=... attribute.

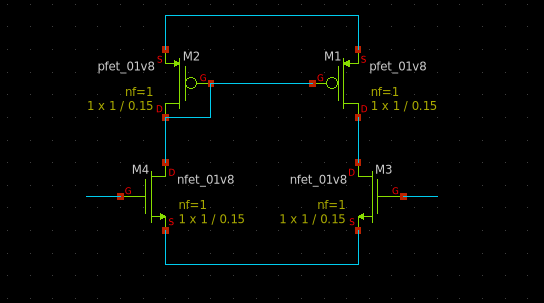

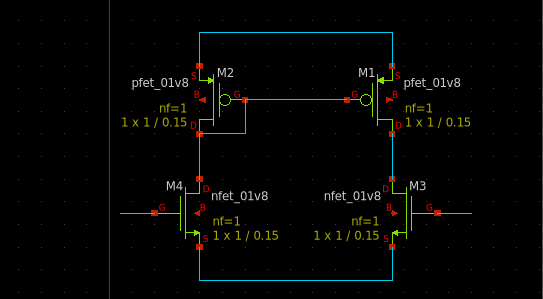

Orientation and mirror meanings are as follows:

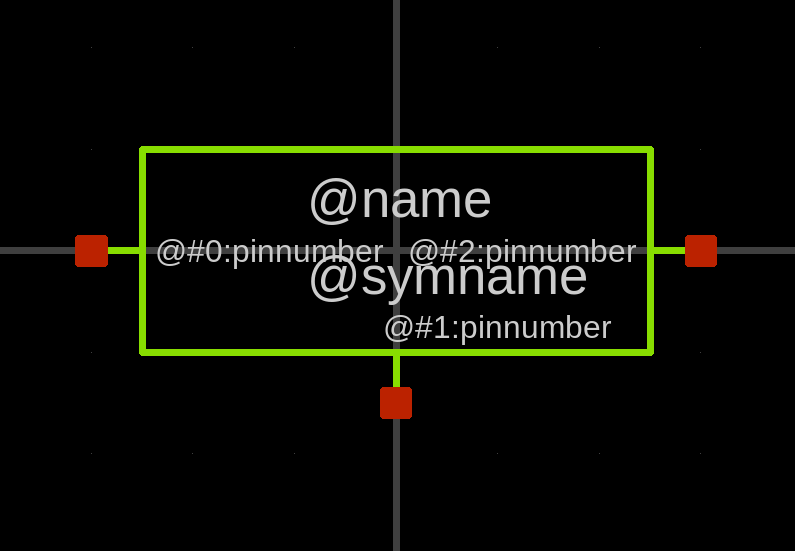

EXAMPLE OF A COMPLETE SYMBOL FILE (7805.sym)

G {}

K {type=regulator

format="x@name @pinlist r@symname"

verilog_format="assign @#2 = @#0 ;"

tedax_format="footprint @name @footprint

device @name @symname"

template="name=U1 footprint=TO220"}

V {}

S {}

E {}

L 4 -60 0 -50 0 {}

L 4 50 0 60 0 {}

L 4 -50 -20 50 -20 {}

L 4 50 -20 50 20 {}

L 4 -50 20 50 20 {}

L 4 -50 -20 -50 20 {}

L 4 0 20 0 30 {}

B 5 -62.5 -2.5 -57.5 2.5 {name=IN dir=in pinnumber=1}

B 5 -2.5 27.5 2.5 32.5 {name=GND dir=inout pinnumber=2}

B 5 57.5 -2.5 62.5 2.5 {name=OUT dir=out pinnumber=3}

T {@name} -17.5 -15 0 0 0.2 0.2 {}

T {@symname} -17.5 0 0 0 0.2 0.2 {}

T {@#0:pinnumber} -47.5 -2.5 0 0 0.12 0.12 {}

T {@#1:pinnumber} -2.5 12.5 0 0 0.12 0.12 {}

T {@#2:pinnumber} 47.5 -2.5 0 1 0.12 0.12 {}

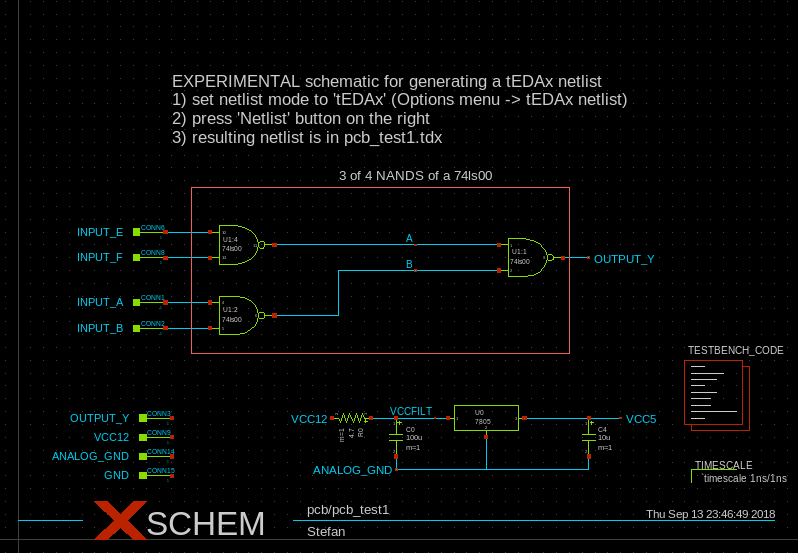

EXAMPLE OF A COMPLETE SCHEMATIC FILE (pcb_test1.sch)

G {}

K {}

V {}

S {}

E {}

B 20 270 -550 860 -290 {}

T {3 of 4 NANDS of a 74ls00} 500 -580 0 0 0.4 0.4 {}

T {EXPERIMENTAL schematic for generating a tEDAx netlist

1) set netlist mode to 'tEDAx' (Options menu -> tEDAx netlist)

2) press 'Netlist' button on the right

3) resulting netlist is in pcb_test1.tdx } 240 -730 0 0 0.5 0.5 {}

N 230 -330 300 -330 {lab=INPUT_B}

N 230 -370 300 -370 {lab=INPUT_A}

N 680 -420 750 -420 {lab=B}

N 680 -460 750 -460 {lab=A}

N 400 -350 440 -350 {lab=B}

N 850 -440 890 -440 {lab=OUTPUT_Y}

N 230 -440 300 -440 {lab=INPUT_F}

N 230 -480 300 -480 {lab=INPUT_E}

N 400 -460 440 -460 {lab=A}

N 550 -190 670 -190 {lab=VCCFILT}

N 590 -130 590 -110 {lab=ANALOG_GND}

N 790 -190 940 -190 {lab=VCC5}

N 890 -130 890 -110 {lab=ANALOG_GND}

N 730 -110 890 -110 {lab=ANALOG_GND}

N 730 -160 730 -110 {lab=ANALOG_GND}

N 590 -110 730 -110 {lab=ANALOG_GND}

N 440 -460 680 -460 {lab=A}

N 500 -420 680 -420 {lab=B}

N 500 -420 500 -350 {lab=B}

N 440 -350 500 -350 {lab=B}

C {title.sym} 160 -30 0 0 {name=l2 author="Stefan"}

C {74ls00.sym} 340 -350 0 0 {name=U1:2 risedel=100 falldel=200}

C {74ls00.sym} 790 -440 0 0 {name=U1:1 risedel=100 falldel=200}

C {lab_pin.sym} 890 -440 0 1 {name=p0 lab=OUTPUT_Y}

C {capa.sym} 590 -160 0 0 {name=C0 m=1 value=100u device="electrolitic capacitor"}

C {74ls00.sym} 340 -460 0 0 {name=U1:4 risedel=100 falldel=200 power=VCC5

url="http://www.engrcs.com/components/74LS00.pdf".sym}

C {LM7805.pdf"}

C {lab_pin.sym} 490 -190 0 0 {name=p20 lab=VCC12}

C {lab_pin.sym} 940 -190 0 1 {name=p22 lab=VCC5}

C {lab_pin.sym} 590 -110 0 0 {name=p23 lab=ANALOG_GND}

C {capa.sym} 890 -160 0 0 {name=C4 m=1 value=10u device="tantalium capacitor"}

C {res.sym} 520 -190 1 0 {name=R0 m=1 value=4.7 device="carbon resistor"}

C {lab_wire.sym} 620 -460 0 0 {name=l3 lab=A}

C {lab_wire.sym} 620 -420 0 0 {name=l0 lab=B}

C {lab_wire.sym} 650 -190 0 0 {name=l1 lab=VCCFILT}

C {connector.sym} 230 -370 0 0 {name=CONN1 lab=INPUT_A verilog_type=reg}

C {connector.sym} 230 -330 0 0 {name=CONN2 lab=INPUT_B verilog_type=reg}

C {connector.sym} 240 -190 0 0 { name=CONN3 lab=OUTPUT_Y }

C {connector.sym} 230 -480 0 0 {name=CONN6 lab=INPUT_E verilog_type=reg}

C {connector.sym} 230 -440 0 0 {name=CONN8 lab=INPUT_F verilog_type=reg}

C {connector.sym} 240 -160 0 0 { name=CONN9 lab=VCC12 }

C {connector.sym} 240 -130 0 0 { name=CONN14 lab=ANALOG_GND verilog_type=reg}

C {connector.sym} 240 -100 0 0 { name=CONN15 lab=GND verilog_type=reg}

C {code.sym} 1030 -280 0 0 {name=TESTBENCH_CODE only_toplevel=false value="initial begin

$dumpfile(\\"dumpfile.vcd\\");

$dumpvars;

INPUT_E=0;

INPUT_F=0;

INPUT_A=0;

INPUT_B=0;

ANALOG_GND=0;

#10000;

INPUT_A=1;

INPUT_B=1;

#10000;

INPUT_E=1;

INPUT_F=1;

#10000;

INPUT_F=0;

#10000;

INPUT_B=0;

#10000;

$finish;

end

assign VCC12=1;

"}

C {verilog_timescale.sym} 1050 -100 0 0 {name=s1 timestep="1ns" precision="1ns" }

XSCHEM COMMAND REFERENCE DOCUMENTATION

The following are xschem specific tcl commands.

All commands are prefixed by the xschem keyword.

Example:

xschem getprop instance x3 OFFSET

- abort_operation

Resets UI state, unselect all and abort any pending operation

place a symbol pin. x,y : pin coordinates name = pin name dir = in|out|inout draw: 1 | 0 (draw or not the added pin immediately, default = 1) if no parameters given start a GUI placement of a symbol pin

Start a GUI placement of a graph object

Ask user to choose a png/jpg file and start a GUI placement of the image

Align currently selected objects to current snap setting

Annotate operating point data into current schematic. use <schematic name>.raw or use supplied argument as raw file to open look for operating point data and annotate voltages/currents into schematic. The optional 'level' integer specifies the hierarchy level the raw file refers to. This is necessary if annotate_op is called from a sub schematic at a hierarchy level > 0 but simulation was done at top level (hierarchy 0, for example) The sim_type optional parameter (specify also file name and level in this case) sets the simulation to look for (instead of default op, dc, tran fallbacks)

if arguments are given (center x and y, radius r, start angle a, end angle b, layer number) place specified arc, otherwise start a GUI placement of an arc. For GUI placement user should click 3 unaligned points to define the arc

Attach net labels to selected component(s) instance(s) Optional integer 'interactive' (default: 0) is passed to attach_labels_to_inst(). setting interactive=2 will place lab_show.sym labels on unconnected instance pins

Start/end bounding box calculation: parameter is either 'begin' or 'end'

Break wires at selected instance pins if '1' is given as 'remove' parameter broken wires that are all inside selected instances will be deleted

Rebuild color palette using values of tcl vars dim_value and dim_bg

Invoke the callback event dispatcher with a software event

Set case insensitive symbol lookup. Use only on case insensitive filesystems

set selected object (instance, wire, line, rect, ...) to position 'n' in its respective array

if descended into a vector instance change inst number we are into to 'n', (same rules as 'descend' command) without going up and descending again if 'draw' string is given redraw screen

check if schematic / symbol file is already opened and return window path

the loaded schematic is in.

for <filename> use absolute path or use [abs_sym_path filename]

window_path[0] == ".drw"

window_path[1] == ".x1.drw"

...

else return empty string

List all used symbols in current schematic and warn if some symbol is newer

Check if all instances have a unique refdes (name attribute in xschem), highlight such instances. If second parameter is '1' rename duplicates

returns index of closest object to mouse coordinates

index = type layer n

type = wire | text | line | poly | rect | arc | inst

layer is the layer number the object is drawn with

(valid for line, poly, rect, arc)

n is the index of the object in the xschem array

example:

$ after 3000 {set obj [xschem closest_object]}

(after 3s)

$ puts $obj

line 4 19

Start a GUI placement of a circle. User should click 3 unaligned points to define the circle

Clear current schematic window. Resets hierarchy level. Remove symbols the 'force' parameter will not ask to save existing modified schematic. the 'schematic' or 'symbol' parameter specifies to default to a schematic or symbol window (default: schematic)

Clears drawing but does not purge symbols

Dim colors or brite colors depending on value parameter: -5 <= value <= 5

Compare currently loaded schematic with another 'sch_file' schematic. if no file is given prompt user to choose one

Select nets/labels connected to currently selected instance if '1' argument is given, stop at wire junctions if '2' argument is given select only wires directly attached to selected instance/net if '3' argument is given combine '1' and '2'

Copy selection to clipboard

Copy hilights hash table from previous schematic to new created tab/window

Copy hierarchy info from tab/window "from" to tab/window "to" Example: xschem copy_hierarchy .drw .x1.drw

if kissing is given add nets to pins that touch other instances or nets if stretch is given stretch connected nets to follow instace pins if dx and dy are given copy selection to specified offset, otherwise start a GUI copy operation

Debug command

Create an xplot file in netlist/simulation directory with the list of highlighted nodes in a format the selected waveform viewer understands (bespice, gaw, ngspice)

enable or disable cursors. cursor will be set at 0.0 position. use 'xschem set cursor[12]_x' to set position n: cursor number (1 or 2, for a or b) e: enable flag: 1: show, 0: hide

Cut selection to clipboard

Set xschem in debug mode.'n' is the debug level (0=no debug). Higher levels yield more debug info.

Delete selection

Bring up a file selector the user can use to delete files

Descend into selected component instance. Optional number 'n' specifies the instance number to descend into for vector instances (default: 0). 0 or 1: leftmost instance, 2: second leftmost instance, ... -1: rightmost instance,-2: second rightmost instance, ... if integer 'notitle' is given pass it to descend_schematic()

Descend into the symbol view of selected component instance

Close all additional windows/tabs. If 'force' is given do not ask for confirmation for changed schematics Returns the remaining # of windows/tabs in addition to main window/tab

Print a list of highlighted objects (nets, net labels/pins, instances) if 'instances' is specified list only instance highlights if 'nets' is specified list only net highlights

Redraw graph rectangle number 'n'. If the optional 'flags' integer is given it will be used as the flags bitmask to use while drawing (can be used to restrict what to redraw)

Redraw only hilight colors on nets and instances the parameter specifies if drawing on window or only on back buffer

Perform DRC rulecheck of instances. if i is specified do check of specified instance otherwise check all instances in current schematic.

Edit xschem file of current schematic if nothing is selected. Edit .sym file if a component is selected.

Edit global schematic/symbol attributes or attributes of currently selected instances

Edit global schematic/symbol attributes or attributes of currently selected instances using a text editor (defined in tcl 'editor' variable)

Embed base 64 encoded 'raw_file' into currently selected element as a 'spice_data' attribute.

Enable/disable layers depending on tcl array variable enable_layer()

escape tcl special characters with backslash if charset is given escape characters in charset

debug function: evaluate arithmetic expression in str

Exit the program, ask for confirm if current file modified. if exit_code is given exit with its value, otherwise use 0 exit code if 'closewindow' is given close the window, otherwise leave with a blank schematic when closing the last remaining window if 'force' is given do not ask before closing modified schematic windows/tabs This command returns the list of remaining open windows in addition to main window

Expand vectored labels/instance names:

xschem expandlabel {2*A[3:0]} --> A[3],A[2],A[1],A[0],A[3],A[2],A[1],A[0] 8

last field is the number of bits

since [ and ] are TCL special characters argument must be quoted with { and }

After setting tcl array pixdata(n) reset fill patterns on all layers If 'nodraw' is given do not redraw window.

Set fill type for layer 'n', fill_type may be 'solid' or 'stipple' or 'empty' If 'nodraw' is given do not redraw window.

Find n-th field string separated by characters in sep. 1st field is in position 1

do not split quoted fields (if quote characters are given) and return unquoted.

xschem find_nth {aaa,bbb,ccc,ddd} {,} 2 --> bbb

xschem find_nth {aaa, "bbb, ccc" , ddd} { ,} {"} 2 --> bbb, ccc

Flip selection horizontally around point x0 y0. if x0, y0 not given use mouse coordinates

Flip selection horizontally, each object around its center

Flip selection vertically around point x0 y0. if x0, y0 not given use mouse coordinates

Flip selection vertically, each object around its center

flatten to current level selected instance texts

Toggle fullscreen modes: fullscreen with menu & status, fullscreen, normal

Get C variable/constant 'var'

- backlayer number of background layer

- bbox bounding box schematic

- bbox_hilighted bounding box of highlinhted objects

- bbox_selected bounding box of selected objects

- build_date time and date this file was built.

- cadlayers number of layers

- case_insensitive case_insensitive symbol matching

- change_lw change line width when zooming

- color_ps color postscript flag

- constr_mv color postscript flag

- current_dirname directory name of current design

- current_name name of current design (no library path)

- current_win_path path of current tab/window (.drw, .x1.drw, ...)

- currsch hierarchy level of current schematic (start at 0)

- cursor1_x cursor 1 position

- cursor2_x cursor 2 position

- debug_var debug level (0 = no debug, 1, 2, 3,...)

- draw_window direct draw into window

- first_sel get data about first selected object

- fix_broken_tiled_fill get drawing method setting (for broken GPUs)

- fix_mouse_coord get fix_mouse_coord setting (fix for broken RDP)

- format alternate format attribute to use in netlist (or NULL)

- graph_lastsel number of last graph that was clicked

- gridlayer layer number for grid

- help command help

- header_text header metadata (license info etc) present in schematic

- infowindow_text ERC messages

- instances number of instances in schematic

- intuitive_interface ERC messages

- last_created_window return win_path of last created tab or window

- lastsel number of selected objects

- line_width get line width

- lines (xschem get lines n) number of lines on layer 'n'

- min_lw minimum line width

- modified schematic is in modified state (needs a save)

- netlist_name netlist name if set. If 'fallback' given get default name

- netlist_type get current netlist type (spice/vhdl/verilog/tedax)

- no_draw disable drawing

- ntabs get number of additional tabs (0 = only one tab)

- pinlayer layer number for pins

- raw_level hierarchy level where raw file was loaded

- rectcolor current layer number

- rects (xschem get rects n) number of rectangles on layer 'n'

- sellayer layer number for selection

- semaphore used for debug

- schname get full path of current sch. if 'n' given get sch of level 'n'

- schprop get schematic "spice" global attributes

- schvhdlprop get schematic "vhdl" global attributes

- schverilogprop get schematic "verilog" global attributes

- schspectreprop get schematic "spectre" global attributes

- schsymbolprop get schematic "symbol" global attributes

- schtedaxprop get schematic "tedax" global attributes

- sch_path get hierarchy path. if 'n' given get hierpath of level 'n'

- sch_to_compare if set return schematic current design is compared with

- sim_sch_path get sim hier path. start from level where raw was loaded

- symbols number of loaded symbols

- temp_dir get windows temporary dir

- text_svg return 1 if using <text> elements in svg export

- textlayer layer number for texts

- top_path get top hier path of current window (always "" for tabbed if)

- topwindow same as top_path but main window returned as "."

- ui_state return UI state

- version return xschem version

- wirelayer layer used for wires

- wires number of wires

- xschem_web_dirname

- xorigin x coordinate of origin

- yorigin y coordinate of origin

- zoom zoom level

create new symbols for instance based implementation selection

return result of get_cell function

return result of get_cell_w_ext function

get the full pathname of "instname" device

modelparam:

0: current, 1: modelparam, 2: modelvoltage

param: device parameter, like ib, gm, vth

set param to {} (empty str) for just branch current of 2 terminal device

for parameters like "vth" modelparam must be 2

for parameters like "ib" modelparam must be 0

for parameters like "gm" modelparam must be 1

getprop instance inst

Get the full attribute string of 'inst'

getprop instance inst attr

Get the value of attribute 'attr'

If 'attr has the form 'cell::sym_attr' look up attribute 'sym_attr'

of the symbol referenced by the instance.

getprop instance_notcl inst attr

Same as above but do not perform tcl substitution

getprop instance_pin inst pin

Get the full attribute string of pin 'pin' of instance 'inst'

Example: xschem getprop instance_pin x3 MINUS --> name=MINUS dir=in

getprop instance_pin inst pin pin_attr

Get attribute 'pin_attr' of pin 'pin' of instance 'inst'

Example: xschem getprop instance_pin x3 MINUS dir --> in

getprop symbol sym_name

Get full attribute string of symbol 'sym_name'

example:

xschem getprop symbol comp_ngspice.sym -->

type=subcircuit

format="@name @pinlist @symname

OFFSET=@OFFSET AMPLITUDE=@AMPLITUDE GAIN=@GAIN ROUT=@ROUT COUT=@COUT"

template="name=x1 OFFSET=0 AMPLITUDE=5 GAIN=100 ROUT=1000 COUT=1p"

getprop symbol sym_name sym_attr [with_quotes]

Get value of attribute 'sym_attr' of symbol 'sym_name'

'with_quotes' (default:0) is an integer passed to get_tok_value()

getprop rect layer num attr [with_quotes]

if '1' is given as 'keep' return backslashes and unescaped quotes if present in value

Get attribute 'attr' of rectangle number 'num' on layer 'layer'

getprop text num attr

Get attribute 'attr' of text number 'num', 'num' can also be the name attribute

of the text object

if 'attr' is 'txt_ptr' return the text string

getprop wire num attr

Get attribute 'attr' of wire number 'num'

('inst' can be an instance name or instance number)

('pin' can be a pin name or pin number)

get schematic associated with instance 'inst' if inst==-1 and a 'symbol' name is given get sch associated with symbol

get "type" value from global attributes of symbol, looking frst in loaded symbols, then looking in symbol file symbols that are not already loaded in the design will not be loaded

get value of token 'tok' in string 'str' 'with_quotes' (default:0) is an integer passed to get_tok_value()

Get length of last looked up attribute name (not its value) if returned value is 0 it means that last searched attribute did not exist

Return various global variables used in the program

Go up one level (pop) in hierarchy if integer 'what' given pass it to the go_back() function what = 1: ask confirm save if current schematic modified. what = 2: do not reset window title

grab root window

Do a simple hash of 'file' 'skip_path_lines' is an integer (default: 0) passed to hash_file()

Do a simple hashing of string 'str'

Print command help

Hierarchical postscript / pdf print if 'file' is not given show a fileselector dialog box

Highlight selected element/pins/labels/nets if 'drill' is given propagate net highlights through conducting elements (elements that have the 'propag' attribute on pins )

Highlight instance 'inst'

if '-fast' is specified do not redraw

'inst' can be an instance name or number

Highlight net name 'net' if '-fast' is given do not redraw hilights after operation

blend_white|blend_black]

Apply required changes to selected images

invert: invert colors

white_transp: transform white color to transparent (alpha=0)

black_transp: transform black color to transparent (alpha=0)

transp_white: transform transparent to white color

transp_black: transform transparent to black color

blend_white: blend with white background and remove alpha

blend_black: blend with black background and remove alpha

write_back: write resulting image back into `image_data` attribute

Place a new instance of symbol 'sym_name' at position x,y, rotation and flip set to 'rot', 'flip' if 'prop' is given it is the new instance attribute string (default: symbol template string) if 'n' is given it must be 0 on first call and non zero on following calls It is used only for efficiency reasons if placing multiple instances

return instance and symbol bounding boxes 'inst' can be an instance name or number

Return instance name, symbol name, x placement coord, y placement coord, rotation and flip

of selected instances

if 'instance' is given (instance name or number) return data about specified instance

Example:

xschem [~] xschem instance_coord

{R5} {res.sym} 260 260 0 0

{C1} {capa.sym} 150 150 1 1

Return a list of 3-items. Each 3-item is

an instance name followed by the symbol reference and symbol type.

Example: xschem instance_list -->

{x1} {sky130_tests/bandgap.sym} {subcircuit}

{...} {...} {...}

...

Return the name of the net attached to pin 'pin' of instance 'inst' Example: xschem instance_net x3 MINUS --> REF

Return the instance name followed by a list of 'pin net' associations example: xschem instance_nodemap x3 --> x3 PLUS LED OUT LEVEL MINUS REF instance x3 pin PLUS is attached to net LED, pin OUT to net LEVEL and so on... If 'pin' is given restrict map to only that pin

Return the position of instance 'inst' in the instance array If 'n' is given set indicated instance position to 'n'

Return the name and coordinates of pin with

attribute 'attr' set to 'value' of instance 'inst'

'inst can be an instance name or a number

Example: xschem instance_pin_coord x3 name MINUS --> {MINUS} 600 -840

Return list of pins of instance 'inst' 'inst can be an instance name or a number

Get number (position) of instance name 'inst'

Return list of instances names and pins attached to net 'net'

Example: xschem instances_to_net PANEL

--> { {Vsw} {plus} {580} {-560} } { {p2} {p} {660} {-440} }

{ {Vpanel1} {minus} {600} {-440} }

tell if 'symbol' is a generator (symbol(param1,param2,...)

line

line gui

if 'x1 y1 x2 y2'is given place line on current

layer (rectcolor) at indicated coordinates.

if 'pos' is given insert at given position in line array.

if 'pos' set to -1 append to last element in line array.

'propstring' is the attribute string. Set to empty if not given.

if 'draw' is set to 1 (default) draw the new object, else don't

If no coordinates are given start a GUI operation of line placement

if `gui` argument is given start a line GUI placement with 1st point

set to current mouse coordinates

set line width to floating point number 'n'

List all schematics at or below current hierarchy with modification times.

Example: xschem list_hiearchy

-->

20230302_003134 {/home/.../ngspice/solar_panel.sch}

20230211_010031 {/home/.../ngspice/pv_ngspice.sch}

20221011_175308 {/home/.../ngspice/diode_ngspice.sch}

20221014_091945 {/home/.../ngspice/comp_ngspice.sch}

Sorted list of non port or non top level current level highlight nets,

separated by character 'sep' (default: space)

if `all_inst` is given list all instance hilights

if `all_nets` is given list all net hilights

if `all` is given list all hash content

List all nets with type (in / out / inout / net)

List tokens in string 'str'

with_quotes:

0: eat non escaped quotes (")

1: return unescaped quotes as part of the token value if they are present

2: eat backslashes

Load a new file 'f'.

'-gui': ask to save modified file or warn if opening an already

open file or opening a new(not existing) file.

'-noundoreset': do not reset the undo history

'-lastclosed': open last closed file

'-lastopened': open last opened file

'-nosymbols': do not load symbols (used if loading a symbol instead of

a schematic)

'-nofullzoom': do not do a full zoom on new schematic.

'-nodraw': do not draw.

'-keep_symbols': retain symbols that are already loaded.

Load schematic in a new tab/window. If 'f' not given prompt user

-lastclosed or -lastopened can be used to open the last closed or last opened file

if 'f' is given as empty '{}' then open untitled.sch

If 'f' is given output stderr messages to file 'f' if 'f' is not given and a file log is open, close log file and resume logging to stderr

Load specified symbol_file

Returns:

>= 0: symbol is already loaded or has been loaded

< 0: symbol was not loaded

write given string to log file, so tcl can write messages on the log file

Get logic state of net named 'net_name' Returns 0, 1, 2, 3 for logic levels 0, 1, X, Z or nothing if no net found.

set 'net_name' to logic level 'n' 'num' times.

'n':

0 set to logic value 0

1 set to logic value 1

2 set to logic value X

3 set to logic value Z

-1 toggle logic valie (1->0, 0->1)

the 'num' parameter is essentially useful only with 'toggle' (-1) value

set selected nets, net labels or pins to logic level 'n' 'num' times.

'n':

0 set to logic value 0

1 set to logic value 1

2 set to logic value X

3 set to logic value Z

-1 toggle logic valie (1->0, 0->1)

the 'num' parameter is essentially useful only with 'toggle' (-1) value

Make a schematic from selected symbol

Create an LCC instance from selection and place it instead of selection also ask if a symbol (.sym) file needs to be created

From current schematic (circuit.sch) create a symbol (circuit.sym) using ipin.sym, opin.sym, iopin.sym in schematic to deduce symbol interface pins.

Merge another file. if 'f' not given prompt user.

resets instance coordinates, and rotaton/flip. A dash will keep existing value if 'nodraw' is given do not draw the moved instance if 'noundo' is given operation is not undoable

Start a move operation on selection and let user terminate the operation in the GUI if kissing is given add nets to pins that touch other instances or nets if stretch is given stretch connected nets to follow instace pins if dx and dy are given move by that amount.

test for my_strtok_r() function

Place a new net label

'type': 1: place a 'lab_pin.sym' label

0: place a 'lab_wire.sym' label

User should complete the placement in the GUI.

Highlight nets attached to selected symbols with a different name than symbol pin

do a netlist of current schematic in currently defined netlist format

if 'filename'is given use specified name for the netlist

if 'filename' contains path components place the file in specified path location.

if only a name is given and no path ('/') components are given use the

default netlisting directory.

This means that 'xschem netlist test.spice' and 'xschem netlist ./test.spice'

will create the netlist in different places.

netlisting directory is reset to previous setting after completing this command

If -messages is given return the ERC messages instead of just a fail (1)

or no fail (0) code.

If -erc is given it means netlister is called from gui, enable show infowindow

If -nohier is given netlist only current level

If -keep_symbols is given no not purge symbols encountered traversing the

design hierarchy

Start a new xschem process for a schematic. If 'f' is given load specified schematic.

Open/destroy a new tab or window

create: create new empty window or with 'file' loaded if 'file' given.

The win_path must be given (even {} is ok).

'1' win_path ({1}) will avoid warnings if opening the

same file multiple times.

destroy: destroy tab/window identified by win_path. Example:

xschem new_schematic destroy .x1.drw

destroy_all: close all tabs/additional windows

if the 'force'argument is given do not issue a warning if modified

tabs are about to be closed.

switch: switch context to specified 'win_path' window or specified schematic name

If 'draw' is given and set to 0 do not redraw after switching tab

(only tab i/f)

if win_path set to "previous" switch to previous schematic.

Main window/tab has win_path set to .drw,

Additional windows/tabs have win_path set to .x1.drw, .x2.drw and so on...

dim schematic to better show highlights

Move origin to 'x, y', optionally changing zoom level to 'zoom'

A dash ('-') given for x or y will keep existing value

debug command to test parse_cmd_string() splits a command string into argv-like arguments return # of args in *argc argv[*argc] is always set to NULL

Debug command to test vector net syntax parser

Paste clipboard. If 'x y' not given user should complete placement in the GUI

List all pins of instance 'inst'

if no 'attr' is given return full attribute string,

else return value for attribute 'attr'.

Example: xschem pinlist x3 name

--> { {0} {PLUS} } { {1} {OUT} } { {2} {MINUS} }

Example: xschem pinlist x3 dir

--> { {0} {in} } { {1} {out} } { {2} {in} }

Example: xschem pinlist x3

--> { {0} {name=PLUS dir=in } } { {1} {name=OUT dir=out } }

{ {2} {name=MINUS dir=in } }

Start a GUI placement operation of specified 'sym_name' symbol. If 'sym_name' not given prompt user 'prop' is the attribute string of the symbol. If not given take from symbol template attribute.

Start a GUI placement of a text object

Start a GUI placement of a polygon if `gui` argument is given start a polygon GUI placement with 1st point set to current mouse coordinates

destroy: will delete preview schematic data and destroy container window close: same as destroy but leave the container window. Used in fileselector to show a schematic preview.

If img_x and img_y are set to 0 (recommended for svg and ps/pdf)

they will be calculated by xschem automatically

if img_x and img_y are given they will set the bitmap size, if

area to export is not given then use the selection boundbox if

a selection exists or do a full zoom.

Export current schematic to image.

img x y size xschem area to export

0 1 2 3 4 5 6 7 8 9

xschem print png file.png [400 300] [ -300 -200 300 200 ]

xschem print svg file.svg [400 300] [ -300 -200 300 200 ]

xschem print ps file.ps [400 300] [ -300 -200 300 200 ]

xschem print eps file.eps [400 300] [ -300 -200 300 200 ]

xschem print pdf file.pdf [400 300] [ -300 -200 300 200 ]

xschem print ps_full file.ps

xschem print pdf_full file.pdf

from highlighted nets/pins/labels:

show == 0 ==> create pins from highlight nets

show == 1 ==> show list of highlight net in a dialog box

show == 2 ==> create labels with i prefix from hilight nets

show == 3 ==> show list of highlight net with path and label

expansion in a dialog box

show == 4 ==> create labels without i prefix from hilight nets

for show = 0, 2, 4 user should complete GUI placement

of created objects

Print spice raw netlist line for instance (number or name) 'inst'

Debug: wrapper to propagate_hilights() function

Push current state on undo stack

what = add | clear | datasets | index | info | loaded | list |

new | points | rawfile | del | read | set | rename |

sim_type | switch | switch_back | table_read | value | values | pos_at | vars |

xschem raw read filename [type [sweep1 sweep2]]

if sweep1, sweep2 interval is given in 'read' subcommand load only the interval

sweep1 <= sweep_var < sweep2

type is the analysis type to load (tran, dc, ac, op, ...). If not given load first found in

raw file.

xschem raw clear [rawfile [type]]

unload given file and type. If type not given delete all type sfrom rawfile

If a number 'n' is given as 'rawfile' delete the 'nth' raw file

if no file is given unload all raw files.

xschem raw del name

delete named vector from current raw file

xschem raw rename old_name new_name

rename a node in the loaded raw file.

xschem raw info

print information about loaded raw files and show the currently active one.

xschem raw new name type sweepvar start end step

create a new raw file with sweep variable 'sweepvar' with number=(end - start) / step datapoints

from start value 'start' and step 'step'

xschem raw list

get list of saved simulation variables

xschem raw vars

get number of simulation variables

xschem raw switch [n | rawfile type]

make the indicated 'rawfile, type' the active one

else if a number n is specified make the n-th raw data the active one.

if no file or number is specified then switch to the next rawdata in the list.

xschem switch_back

switch to previously active rawdata.

xschem raw datasets

get number of datasets (simulation runs)

xschem raw value node n [dset]

return n-th value of 'node' in raw file

dset is the dataset to look into in case of multiple runs (first run = 0).

if dset = -1 consider n as the absolute position into the whole data file

(all datasets combined).

If n is given as empty string {} return value at cursor b,

dset not used in this case

xschem raw loaded

return hierarchy level where raw file was loaded or -1 if no raw loaded

xschem raw rawfile

return raw filename

xschem raw sim_type

return raw loaded simulation type (ac, op, tran, ...)

xschem raw index node

get index of simulation variable 'node'.

Example: raw index v(led) --> 46

xschem raw values node [dset]

print all simulation values of 'node' for dataset 'dset' (default dset=0)

dset= -1: print all values for all datasets

xschem raw pos_at node value [dset] [from_start] [to_end]

returns the position, starting from 0 or from_start if given, to the end of dataset

or to_end if given of the first point 'p' where node[p] and node[p+1] bracket value.

If dset not given assume dset 0 (first one)

This is usually done on the sweep (time) variable in transient sims where timestep is

not uniform

xschem raw points [dset]

print simulation points for dataset 'dset' (default: all dataset points combined)

xschem raw set node n value [dset]

change loaded raw file data node[n] to value

dset is the dataset to look into in case of multiple runs (first run = 0)

dset = -1: consider n as the absolute position in the whole raw file

(all datasets combined)

xschem raw table_read tablefile

read a tabular data file.

First line is the header line containing variable names.

data is presented in column format after the header line

First column is sweep (x-axis) variable

Double empty lines start a new dataset

Single empty lines are ignored

Datasets can have different # of lines.

new dataset do not start with a header row.

Lines beginning with '#' are comments and ignored

time var_a var_b var_cnode in the loaded raw file.

# this is a comment, ignored

0.0 0.0 1.8 0.3

<single empty line: ignored>

0.1 0.0 1.5 0.6

... ... ... ...

<empty line>

<Second empty line: start new dataset>

0.0 0.0 1.8 0.3

0.1 0.0 1.5 0.6

... ... ... ...

xschem raw add varname [expr] [sweep_var]

add a 'varname' vector with all values set to 0 to loaded raw file if expr not given

otherwise initialize data with values calculated from expr.

if expr is given and also sweep_var is given use indicated sweep_var for expressions

that need it. If sweep_var not given use first raw file variable as sweep variable.

If varname is already existing and expr given recalculate data

Example: xschem raw add power {outm outp - i(@r1[i]) *}

Unload all simulation raw files You can use xschem raw clear as well.

If a raw file is already loaded delete from memory then load specified file and analysis 'sim' (dc, ac, tran, op, ...) If 'sim' not specified load first section found in raw file. if sweep1, sweep2 interval is given load only the interval sweep1 <= sweep_var < sweep2

If a simulation raw file is already loaded delete from memory else read section 'sim' (tran, dc, ac, op, ...) of base64 encoded data from a 'spice_data' attribute of selected instance If sim not given read first section found

Rebuild logical connectivity abstraction of schematic

Rebuild selection list

call the record_global_node function (list of netlist global nodes)

rect [x1 y1 x2 y2] [pos] [propstring] [draw]

if 'x1 y1 x2 y2'is given place recangle on current

layer (rectcolor) at indicated coordinates.

if 'pos' is given insert at given position in rectangle array.

if 'pos' set to -1 append rectangle to last element in rectangle array.

'propstring' is the attribute string. Set to empty if not given.

if 'draw' is set to 1 (default) draw the new object, else don't

rect

If no coordinates are given start a GUI operation of rectangle placement

rect gui

if `gui` argument is given start a GUI placement of a rectangle with 1st

point starting from current mouse coordinates

Redo last undone action

redraw window

Forced (be careful!) Reload current schematic from disk

Reload all used symbols from disk

Internal command: remove all symbol definitions

Replace 'inst' symbol with 'new_symbol'

If doing multiple substitutions set 'fast' to {}

on first call and 'fast' on next calls

for faster operation.

do a 'xschem redraw' at end to update screen

Example: xschem replace_symbol R3 capa.sym

Reset cached instance and symbol cached flags (inst->flags, sym->flags)

Reset instance attribute string taking it from symbol template string

This is a low level command, it merely changes the xctx->inst[...].name field. It is caller responsibility to delete all symbols before and do a reload_symbols afterward

internal command: calls resetwin()

if 'net' is given return its topmost full hierarchy name else returns the topmost full hierarchy name of selected net/pin/label. Nets connected to I/O ports are mapped to upper level recursively

Rotate selection around point x0 y0. if x0, y0 not given use mouse coordinates

Rotate selected objects around their 0,0 coordinate point

round number 'i' to 'n' digits

Save schematic if modified. Does not ask confirmation! if 'fast' is given it is passed to save_schematic() to avoid updating window/tab/sim button states

save current schematic as 'file'

if file is empty ({}) use current schematic name

as defalt and prompt user with file selector

'type' is used used to set/change file extension:

schematic: save as schematic (*.sch)

symbol: save as symbol (*.sym)

If not specified default to schematic (*.sch)

Does not ask confirmation if file name given

List a 2-item list of all pins and directions of current schematic

Example: xschem sch_pinlist

--> {PLUS} {in} {OUT} {out} {MINUS} {in} {VCC} {inout} {VSS} {inout}

When a symbol is selected edit corresponding schematic in a new tab/window if not already open. If nothing selected open another window of the second schematic (issues a warning). if 'new_process' is given start a new xschem process if 'nodraw' is given do not draw loaded schematic returns '1' if a new schematic was opened, 0 otherwise

Search instances / wires / rects / texts with attribute string containing 'tok'

and value 'val'

search can be exact ('exact') or as a regular expression ('regex')

select:

0 : highlight matching instances

1 : select matching instances

-1 : unselect matching instances

'tok' set as:

propstring : will search for 'val' in the entire

*instance* attribute string.

cell::propstring : will search for 'val' in the entire

*symbol* attribute string.

cell::name : will search for 'val' in the symbol name

cell::<attr> will search for 'val' in symbol attribute 'attr'

example: xschem search regex 0 cell::template GAIN=100

if 'no_match_case' is specified do not consider case sensitivity in search

if 'nodraw' is specified do not draw search result

select rect|line|poly|arc layer id [clear] [fast]

Select indicated instance or wire or text, or

Select indicated (layer, number) rectangle, line, polygon, arc.

For 'instance' 'id' can be the instance name or number

for all other objects 'id' is the position in the respective arrays

if 'clear' is specified does an unselect operation

if 'fast' is specified avoid sending information to infowindow and status bar

if 'nodraw' is given do not draw selection

returns 1 if something selected, 0 otherwise

Selects all objects in schematic

Select all nets/labels that are dangling, ie not attached to any non pin/port/probe components Returns number of selected items (wires,labels) if danglings found, 0 otherwise

Select all highlight objects (wires, labels, pins, instances)

Select all objects inside the indicated area if [sel] is set to '0' do an unselect operation

Return a list of selected instance names If what is not given or set to 'inst' return list of selected instance names If what set to 'rect' return list of selected rectangles with their coordinates If what set to 'text' return list of selected texts with their coordinates

Return list of selected nets

Send selected wires/net labels/pins/voltage source or ammeter currents to current open viewer (gaw or bespice)

Set C variable 'var' to 'value'

- cadgrid set cad grid (default: 20)

- cadsnap set mouse snap (default: 10)

- change_lw allow change line width when zooming

- color_ps set color psoscript (1 or 0)

- crosshair_layer set layer for mouse crosshair

- constr_mv set constrained move (1=horiz, 2=vert, 0=none)

- cursor1_x set graph cursor1 position

- cursor2_x set graph cursor2 position

- draw_window set drawing to window (1 or 0)

- fix_broken_tiled_fill alternate drawing method for broken GPUs

- fix_mouse_coord fix for wrong mouse coords in RDP software

- format set name of custom format attribute used for netlisting

- header_text set header metadata (used for license info)

- hide_symbols set to 0,1,2 for various hiding level of symbols

- hilight_color set hilight color for next hilight

- infowindow_text ERC messages

- intuitive_interface set intuitive interface

- line_width set line width

- netlist_name set custom netlist name

- netlist_type set netlisting mode (spice, verilog, vhdl, tedax, symbol)

- no_draw set no drawing flag (0 or 1)

- no_undo set to 1 to disable undo

- raw_level set hierarchy level loaded raw file refers to

- rectcolor set current layer (0, 1, .... , cadlayers-1)

- sch_to_compare set name of schematic to compare current window with

- schsymbolprop set global symbol attribute string

- schprop set schematic global spice attribute string

- schverilogprop set schematic global verilog attribute string

- schspectreprop set schematic global spectre attribute string

- schvhdlprop set schematic global vhdl attribute string

- schtedaxprop set schematic global tedax attribute string

- text_svg set to 1 to use svg <text> elements

- semaphore debug

- show_hidden_texts set to 1 to enable showing texts with attr hide=true

- sym_txt set to 0 to hide symbol texts

Return string 'str' replacing/adding/removing tokens that are different between 'new_str' and 'old_str'

Force modify status on current schematic integer 'n': 0 : clear modified flag, update title and tab names, upd. simulation button colors. 1 : set modified flag, update title and tab names, upd. simulation button colors, rst floater caches. 2 : clear modified flag, do nothing else. 3 : set modified flag, do nothing else. -1 : set title, rst floater caches. -2 : rst floater caches, update simulation button colors (Simulate, Waves, Netlist).

setprop [-fast] instance inst [tok] [val]

set attribute 'tok' of instance (name or number) 'inst' to value 'val'

If 'tok' set to 'allprops' replace whole instance prop_str with 'val'

If 'val' not given (no attribute value) delete attribute from instance

If 'tok' not given clear completely instance attribute string

If '-fast' argument if given does not redraw and is not undoable

setprop symbol name tok [val]

Set attribute 'tok' of symbol name 'name' to 'val'

If 'val' not given (no attribute value) delete attribute from symbol

This command is not very useful since changes are not saved into symbol

and netlisters reload symbols, so changes are lost anyway.

setprop rect [-fast|-fastundo] lay n tok [val]

Set attribute 'tok' of rectangle number'n' on layer 'lay'

If 'val' not given (no attribute value) delete attribute from rect

If '-fast' argument is given does not redraw and is not undoable

If '-fastundo' s given same as above but action is undoable.

setprop rect 2 n fullxzoom

setprop rect 2 n fullyzoom

These commands do full x/y zoom of graph 'n' (on layer 2, this is hardcoded).

setprop wire [-fast|-fastundo] n tok [val]

Set attribute 'tok' of wire number'n'

If 'val' not given (no attribute value) delete attribute from wire

If '-fast' argument is given does not redraw and is not undoable

If '-fastundo' s given same as above but action is undoable.

setprop [-fast|-fastundo] text n [tok] [val]

Set attribute 'tok' of text number 'n'

If 'tok' not specified set text string (txt_ptr) to value

If "txt_ptr" is given as token replace the text txt_ptr ("the text")

If 'val' not given (no attribute value) delete attribute from text

If '-fast' argument is given does not redraw and is not undoable

If '-fastundo' is given same as above but action is undoable.

Add a "lab_show.sym" to all instance pins that are not connected to anything

Run a simulation (start simulator configured as default in Tools -> Configure simulators and tools) If 'callback' procedure name is given execute the procedure when simulation is finished. all execute(..., id) data is available (id = execute(id) ) A callback prodedure is useful if simulation is launched in background mode ( set sim(spice,1,fg) 0 )

Start a GUI start snapped wire placement (click to start a wire to closest pin/net endpoint)

replace 'rep' with 'with' in string 'str' if rep not preceeded by an 'escape' character

Return string 'str' with 'tok' attribute value replaced with 'newval'

Return the base_name field of a symbol with name or number `n` Normally this is empty. It is set for overloaded symbols, that is symbols derived from the base symbol due to instance based implementation selection (the instance `schematic` attribute)

When a symbol is selected edit it in a new tab/window if not already open. If nothing selected open another window of the second schematic (issues a warning). if 'new_process' is given start a new xschem process

swap cursor A (1) and cursor B (2) positions.

swap first and second window in window interface (internal command)

Switch context to indicated window path or schematic name returns 0 if switch was successfull or 1 in case of errors if "previous" given as window path switch to previously active tab (only for tabbed interface) (no tabs/windows present or no matching win_path / schematic name found).

if 'n' given list symbol with name or number 'n', else list all if 'derived_symbols' is given list also symbols derived from base symbol due to instance based implementation selection. This option must be used after a netlist operation with 'keep_symbols' TCL variable set to 1

list all windows / tabs with window pathname and associated filename

If a simulation raw file is lodaded unload from memory.

else read a tabular file 'table_file'

First line is the header line containing variable names.

data is presented in column format after the header line

First column is sweep (x-axis) variable

Double empty lines start a new dataset

Single empty lines are ignored

Datasets can have different # of lines.

new dataset do not start with a header row.

Lines beginning with '#' are comments and ignored

time var_a var_b var_c

# this is a comment, ignored

0.0 0.0 1.8 0.3

<single empty line: ignored>

0.1 0.0 1.5 0.6

... ... ... ...

<empty line>

<Second empty line: start new dataset>

0.0 0.0 1.8 0.3

0.1 0.0 1.5 0.6

... ... ... ...

Testmode ...

Create a text object

x, y, rot, flip specify the position and orientation

text is the text string

props is the attribute string

size sets the size

draw is a flag. If set to 1 will draw the created text

get text string of text object 'n'

Toggle dark/light colorscheme

toggle *_ignore=true attribute on selected instances

* = {spice,verilog,vhdl,tedax} depending on current netlist mode

returns 1 if line {x1 y1 x2 y2} touches point {x0 y0}, 0 otherwise

Translate string 'str' replacing @xxx tokens with values in instance 'n' attributes

Example: xschem translate vref {the voltage is @value}

the voltage is 1.8

If -1 is given as the instance number try to translate the string without using any

instance specific data

Translate string 'str' replacing @xxx tokens with values in string s1 or if

not found in string s2 or if not found in string s3

eat_escapes should be either 1 (remove backslashes) or 0 (keep them)

Example: xschem translate3 {the voltage is @value} {name=x12} {name=x1 value=1.8}

the voltage is 1.8

Remove leading and trailing chars matching any character in 'sep' from str

Remove operlapping wires, join lines, trim wires at intersections

Undo last action. Optional integers redo and set_modify are passed to pop_undo()

Use disk file ('disk') or RAM ('memory') for undo bufer

if 'fast' is given do not redraw Clear all highlights

Unhighlight selected nets/pins

Unselect everything. If draw is given and set to '0' no drawing is done

Unselect objects (not symbol instances) attached to some instance with a non empty name=... attribute

Update all symbol bounding boxes

update tcl ngspice::ngspice array data from raw file point 0

View attributes of selected element (read only) if multiple selection show the first element (in xschem array order)

Highlight or select (if 'sel' set to 1) perfectly overlapped instances this is usually an error and difficult to grasp visually

Used by xschem.tcl for configure events (set icon)

return 4 coordinates of wire[n]

wire wire gui Place a new wire if no coordinates are given start a GUI wire placement if `gui` argument is given start a GUI placement of a wire with 1st point starting from current mouse coordinates

start a wire cut operation. Point the mouse in the middle of a wire and Alt-click right button. if x and y are given cut wire at given point if noalign is given and is set to 'noalign' do not align the cut point to closest snap point

For debug

Zoom to specified coordinates, if 'factor' is given reduce view (factor < 1.0) or add border (factor > 1.0) If no coordinates are given start GUI zoom box operation

Set full view. If 'center' is given center vire instead of lower-left align If 'nodraw' is given don't redraw If 'nolinewidth]' is given don't reset line widths.

Zoom to highlighted objects

Zoom in drawing

Zoom out drawing

Zoom to selection

XSCHEM TCL GLOBAL VARIABLES

# default command for first spice simulation command (interactive ngspice)

sim(spice,0,cmd) {$terminal -e 'ngspice -i "$N" -a || sh'}

# flag for foreground (1) or background (0) operation

sim(spice,0,fg) 0

# flag for status dialog box opening (1) at simulation end or not (0)

sim(spice,0,st) 0

sim(spice,1,cmd) {ngspice -b -r "$n.raw" -o "$n.out" "$N"}

sim(spice,1,fg) 0

sim(spice,1,st) 1

sim(spice,2,cmd) "Xyce \"\$N\"\n# Add -r \"\$n.raw\" if you want all variables saved"

sim(spice,2,fg) 0

sim(spice,2,st) 1

sim(spice,3,cmd) {mpirun /path/to/parallel/Xyce "$N"}

sim(spice,3,fg) 0

sim(spice,3,st) 1

# Number of configured spice simulation commands (4), [ sim(spice,0,...) ... sim(spice,3,...) ]

sim(spice,n) 4

# default spice command to use (0) --> sim(spice,0,...)

sim(spice,default) 0

sim(spicewave,0,cmd) {gaw "$n.raw" }

sim(spicewave,0,fg) 0

sim(spicewave,0,st) 0

sim(spicewave,1,cmd) {$terminal -e ngspice}

sim(spicewave,1,fg) 0

sim(spicewave,1,st) 0

sim(spicewave,2,cmd) {rawtovcd -v 1.5 "$n.raw" > "$n.vcd" && gtkwave "$n.vcd" "$n.sav" 2>/dev/null}

sim(spicewave,2,fg) 0

sim(spicewave,2,st) 0

sim(spicewave,3,cmd) {$env(HOME)/analog_flavor_eval/bin/bspwave --socket localhost $bespice_listen_port "$n.raw" }

sim(spicewave,3,fg) 0

sim(spicewave,3,st) 0

sim(spicewave,n) 4

sim(spicewave,default) 0

# list of configured tools. For each of these there is a set of sim(tool,...) settings

sim(tool_list) spice spicewave verilog verilogwave vhdl vhdlwave

sim(verilog,0,cmd) {iverilog -o .verilog_object -g2012 "$N" && vvp .verilog_object}

sim(verilog,0,fg) 0

sim(verilog,0,st) 1

sim(verilog,n) 1

sim(verilog,default) 0

sim(verilogwave,0,cmd) {gtkwave dumpfile.vcd "$N.sav" 2>/dev/null}

sim(verilogwave,0,fg) 0

sim(verilogwave,0,st) 0

sim(verilogwave,n) 1

sim(verilogwave,default) 0

sim(vhdl,0,cmd) {ghdl -c --ieee=synopsys -fexplicit "$N" -r "$s" --wave="$n.ghw"}

sim(vhdl,0,fg) 0

sim(vhdl,0,st) 1

sim(vhdl,n) 1

sim(vhdl,default) 0

sim(vhdlwave,0,cmd) {gtkwave "$n.ghw" "$N.sav" 2>/dev/null}

sim(vhdlwave,0,fg) 0

sim(vhdlwave,0,st) 0

sim(vhdlwave,n) 1

sim(vhdlwave,default) 0

add_all_windows_drives 1

autofocus_mainwindow 1

auto_hilight 0

autotrim_wires 0

bespice_listen_port {}

bespice_server_getdata

big_grid_points 0

bus_replacement_char {} ;# use {<>} to replace [] with <> in bussed signals

cadlayers 22

cairo_font_line_spacing 1.0

cairo_font_name {Sans-Serif}

cairo_font_scale 1.0

cairo_vert_correct 0

case_insensitive 0

change_lw 1

color_ps 1

colors $dark_colors

compare_sch 0

component_browser_on_top 1

connect_by_kissing 0

constrained_move 0

copy_cell 0

dark_colors {

"#000000" "#00ccee" "#3f3f3f" "#cccccc" "#88dd00" "#bb2200" "#00ccee" "#ff0000"

"#ffff00" "#ffffff" "#ff00ff" "#00ff00" "#0044dd" "#aaaa00" "#aaccaa" "#ff7777"

"#bfff81" "#00ffcc" "#ce0097" "#d2d46b" "#ef6158" "#fdb200"}

dark_colorscheme 1

dark_colors_save

debug_var 0

delay_flag

dim_bg 0.0

dim_value 0.0

dircolor(/share/doc/xschem/) {#338844}

dircolor(/share/xschem/) red

disable_unique_names 0

download_url_helper {curl -f -s -O}

draw_grid 1

draw_window 0

editor {gvim -f}

edit_prop_size 80x12

edit_symbol_prop_new_sel {}

enable_dim_bg 0

enable_layer($i) 1

enable_stretch 0

en_hilight_conn_inst 0

execute(cmd,<id>)

execute(data,<id>)

execute(status,<id>)

execute(cmd,last)

execute(data,last)

execute(status,last)

execute(error,last)

execute(exitcode,last)

execute(id)

flat_netlist 0

fullscreen 0

gaw_tcp_address {localhost 2020}

graph_bus 0

graph_logx 0

graph_logy 0

graph_rainbow 0

graph_raw_level -1 ;# hierarchy level where raw file has been loaded

graph_schname {}

graph_sel_color 4

graph_selected {}

graph_sel_wave {}

graph_sort 0

has_cairo 1

has_x

hide_empty_graphs 0 ;# if set to 1 waveform boxes will be hidden if no raw file loaded

hide_symbols 0

incr_hilight 1

# text saved into the ERC informational dialog box.

# netlist warnings and errors are shown here.

infowindow_text

initial_geometry {900x600}

launcher_default_program {xdg-open}

light_colors {

"#ffffff" "#0044ee" "#aaaaaa" "#222222" "#229900" "#bb2200" "#00ccee" "#ff0000"

"#888800" "#00aaaa" "#880088" "#00ff00" "#0000cc" "#666600" "#557755" "#aa2222"

"#7ccc40" "#00ffcc" "#ce0097" "#d2d46b" "#ef6158" "#fdb200"}

light_colors_save

line_width 0

live_cursor2_backannotate 0

# if set use <sch_dir>/simulation for netlist and sims

local_netlist_dir 0

lvs_ignore 0

lvs_netlist 0

measure_text "y=\nx="

menu_debug_var 0

myload_files2 {}

myload_globfilter {*}

myload_index1 0

netlist_dir "$USER_CONF_DIR/simulations"

netlist_show 0

netlist_type spice

nocairo_font_xscale .85

nocairo_font_yscale .88

nocairo_vert_correct 0

no_change_attrs 0

nolist_libs {}

noprint_libs {}

only_probes 0 ; # 20110112

OS

persistent_command 0

preserve_unchanged_attrs 0

rainbow_colors 0

search_schematic 0

show_hidden_texts 0

show_infowindow 0

show_infowindow_after_netlist 0

show_pin_net_names 0

spiceprefix 1

split_files 0

svg_font_name {Sans-Serif}

symbol_width 150

sym_txt 1

tabbed_interface 0

tcl_files {}

tclstop 0

terminal xterm

text_line_default_geometry 80x12

textwindow_wcounter

toolbar_horiz 1

toolbar_list { ... }

toolbar_visible 0

to_pdf {ps2pdf}

to_png {gm convert}

transparent_svg 0

undo_type disk

unzoom_nodrift 0

use_tclreadline 1 ;# use the tclreadline package for command prompt. default: 1

USER_CONF_DIR

verilog_2001 1

verilog_bitblast 0

viewdata_wcounter

xschem_libs {}

xschem_listen_port {}

xschem_server_getdata

XSCHEM_SHAREDIR

XSCHEM_START_WINDOW {}

XSCHEM_TMP_DIR {/tmp}

zoom_full_center 0

Simulator / waveform setup

In xschem a tcl array variable sim is used to specify external process commands, like simulators and waveform viewers. This variable is set in the GUI with the Simulation-> Configure simulators and tools menu entry. First of all you need to set the tool_list list of configured tools:

set sim(tool_list) { spice spicewave verilog verilogwave vhdl vhdlwave }

For each tool you need to define some sub elements:

# Number of configured spice simulation commands (4), [ sim(spice,0,...) ... sim(spice,3,...) ]

sim(spice,n) 4

# default spice command to use (0) --> sim(spice,0,...)

sim(spice,default) 0

# default command for first spice simulation command (interactive ngspice)

sim(spice,0,cmd) {$terminal -e 'ngspice -i "$N" -a || sh'}

# flag for foreground (1) or background (0) operation

sim(spice,0,fg) 0

# flag for status dialog box opening (1) at simulation end or not (0)

sim(spice,0,st) 0

sim(spice,1,cmd) {ngspice -b -r "$n.raw" -o "$n.out" "$N"}

sim(spice,1,fg) 0

sim(spice,1,st) 1

sim(spice,2,cmd) "Xyce \"\$N\"\n# Add -r \"\$n.raw\" if you want all variables saved"

sim(spice,2,fg) 0

sim(spice,2,st) 1

sim(spice,3,cmd) {mpirun /path/to/parallel/Xyce "$N"}

sim(spice,3,fg) 0

sim(spice,3,st) 1

XSCHEM TCL PROCEDURES

Commands in brackets are internal procedures, not supposed to be used by end users

# show xschem about dialog

about

# given a symbol reference 'sym' return its absolute path

# Example: % abs_sym_path devices/iopin.sch

# /home/schippes/share/xschem/xschem_library/devices/iopin.sym

abs_sym_path sym

add_ext

add_lab_no_prefix

add_lab_prefix

# show an alert dialog box and display 'text'.

# if 'position' is empty (example: alert_ {hello, world} {}) show at mouse coordinates

# otherwise use specified coordinates example: alert_ {hello, world} +300+400

# if nowait is 1 do not wait for user to close dialog box

# if yesnow is 1 show yes and no buttons and return user choice (1 / 0).

# (this works only if nowait is unset).

alert_ text [position] [nowait] [yesno]

ask_save

attach_labels_to_inst

balloon

balloon_show

bespice_getdata

bespice_server

build_widgets

change_color

clear_simulate_button

color_dim

context_menu

convert_to_pdf

convert_to_png

create_layers_menu

create_pins

# pause execution for 'ms milliseconds, keeping event loop responding

delay [ms]

delete_ctx

delete_files

delete_tab

descend_hierarchy

download_url

edit_file

edit_netlist

edit_prop

edit_vi_netlist_prop

edit_vi_prop

enter_text